Raltron晶振公司常见的感应振荡器技术(二)

上一篇我们讲了倒置台面晶体和水晶选择等内容,初步了解了Raltron晶振的频率控制元器件技术研究,在晶体这个领域欧美国家始终比较在行,并且目前仍然还在不断的开发和科研。Raltron公司面向的客户群体主要有无线通信,汽车制造,广播音频,数码电子,全球导航定位系统,工业仪器等模块。不仅为来自各个地区的用户提供品质好的晶振产品,还为客户解决一系列晶体/振荡器相关的难题,提供适用的晶振解决方案,为每一位客户排忧解难!

带状水晶系列:

ASIC CELLS振荡器基础。今天使用最广泛的振荡器是MOS门振荡器使用无缓冲逆变器。几乎所有的微处理器都在与许多其他数字应用程序一样这个电路内置在电池内或被驱动来自使用该ASIC的外部振荡器电路。

石英晶体振荡器单元具有几个特征这对振荡器设计师很重要。Rin Rin高-10兆欧姆击溃。Rout取决于逻辑类型正在使用。ECL逻辑具有低阻抗-在7欧姆的范围内。CMOS逻辑有更高的输出阻抗-在700欧姆。HCMOS逻辑通常是介于250和500欧姆之间。一个振荡器设计师应该获得输出来自的阻抗信息制造商。如果没有这个信息可用,简单的输出阻抗测试。

电路如图2所示。获得。通过偏置逆变器得到增益在线性模式下。偏见是通过连接逆变器的电阻器输出到输入。此连接导致高增益和宽带宽,但都缺乏一致性。

相移:

f0处的相移,频率振荡大约是180度通过放大器从输入到输出。导出额外的180度相位来自pi反馈网络。保险可靠的启动和稳定的运行,电路必须具有相移的能力比180更远20度学位最低反馈要求。

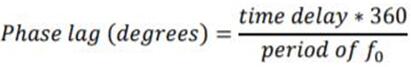

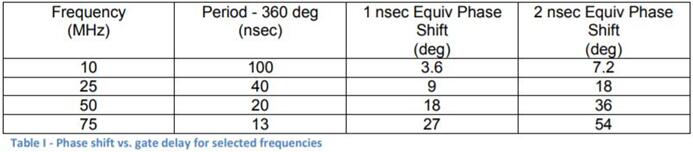

通过时间延迟修改相移从放大器的输入到输出-通常为1至2纳秒。以来频率是时间,时间的倒数延迟等于额外的相移逆变器。外部pi电路必须比延迟小180度等同移位。表I显示了1和2的相移选定频率下的纳秒延迟。这种减少的相移信息将是在波德图分析中很有用。

设计师应该确保有足够的动态范围来弥补元件或电源变化。对于例如,电路中的手指会打扰相移并允许石英晶振启动,锁定继续,并继续振荡。为了满足巴克豪森的相移标准,我们必须在外部移动180度(加上一个至少25个附加度)反馈回路。设计稳定振荡器,希望具有快速的相位变化率在180度点。在整个过程中获得180度相移pi网络,我们需要相移90水晶两端的度数。在ASIC输入侧的晶体,晶体流入C1的电流如果变为90度津很高。在ASIC输出端晶体,应该进行相移通过90度,效果较差从逆变器的时间延迟相移-参考表1。基本反馈电路。一个基本的皮尔斯OSC晶振电路如图3所示。组件包括相移元素C1和C2以及输出阻抗调节电阻,Rx。注意Rx是分立电路元件而不是包含在输出阻抗中逆变器。如果振荡器设计中省略了Rx(不幸的是很多次),容易出现问题。设计师应该总是为这个组件布置他的电路如果Rx是,则使用零欧姆电阻(短路)他的反馈配置不需要。反馈元素选择。为了这纸,ASIC单元外部的反馈将被缩减为“pi”或平行坦克组态。值得注意的是“T”配置有类似的特点但是不属于本文范围。那里是四(4)种可能的组合非负载可能发生的电抗坦克电路。这四个案例是如图4所示。

图4,情况1,两腿都有电容器和相互连接的电感器。该电路只有在电感器振荡时才会振荡放在Z3的位置。一个例子案例1是常见的Pierce配置常用于有源晶振电路。连接晶体可以满足振荡要求条件略高于每个晶体上的Fs模式。电路将捕获模式具有最低的实际期限。大多数时候频谱,晶体是电容性和无振荡。

电抗与参考图5晶体谐振器的频率响应。如果a,则情况2和3都不能振荡电容器或电感器是外部的是连接的。如果是电容器,情况4可以振荡连接在终端之间。水晶的连接可能不是因为晶体的电抗是有效的大部分频率都是电容性的光谱。振荡可以在多个时发生因为晶体可以满足频率所需阻抗均低于Fs和以上法。在这方面一定要小心组态。

阻抗匹配。振荡器电路取决于阶段的变化率稳定性。阶段性变化的重要性可以用图形方式看到当考虑到频率的变化时扰动,组件变化,潮湿,上帝的行为等。振荡器会不满足巴克豪森的阶段标准旧的频率,所以它改变阶段,直到振荡可能发生。假设不稳定电路转换阶段2度。这可能导致频率改变为6Hz或相位斜率为1/3度/Hz。通常,我们希望进口晶振每Hz的相位斜率为40度。如果在输入端进行阻抗匹配并且输出pi网络,相位斜率大大降低了因此,设计师应该争取一个大的不匹配最大化相位斜率。这一切都必须完成控制中的常识。作为阻抗匹配的一个例子,考虑在110中插入一个电容器伏墙插座和试图移动电力公司的阶段。显然,这个不起作用,因为信号源有非常非常低的阻抗。如果是一个系列插入电阻器的电阻相等对电容器的电抗,相位在R-C处换档为45度结和信号幅度将是减少½。

同样的现象发生在ASIC的输出。如果欧美晶振输出阻抗与外部电抗相比较低,电容器不会明显偏移相。陈述更简单,一个小C2连接到低阻抗输出ASIC什么都不做。如果添加Rx,则(Rx=XC2)45度相移将发生在水晶。可能是最重要的本文的考虑是选择C2相对于输出阻抗ASIC单元。参考图6。观察到如果Rx是短路,则Rout是直接的与C2并行。输出的Q值匹配网络定义为Rout+Rx除以XC2。教科书需要Q版10.考虑妥协并让Q≈仅2.如果上述电路工作在40MHz和单元具有输出阻抗200欧姆,C2应该是39pf-不是不合理。如果ECL门与a一起使用Q为1,C2应为560pf-即不合理。

使用戴维宁相当于输出司机,人们可以认识到这个阶段在输出端移位-C2连接非常多一个函数C2的选择。使用相当于Norton,我们观察到了输出阻抗直接跨C2。底线。如果Q小于2,则增加Rx或增加C2-在限制范围内。接受Q.最低=2。最低Q=5的设计。ASIC驱动能力。驱动器必须具备ASIC单元的能力考虑选择组件。该电容器电流(i)=dQ/dt,因此Q=∫I*DT。然后电压是积分I*DT/℃。输出驱动程序必须能够在短时间内充电C2。如果C2是小,它可以很快充电;但是,如果C2更大,ASIC输出驱动器具有限制gm,电容器不会充电显着和电压发展C2将非常有限。

来自电池的输出信号不仅如此从外部驱动C2,但也是一样的信号驱动下一个内部逻辑用于生成系统的元素时钟信号。如果这个信号很小的话振幅,应引起关注。逻辑电平应从20%切换到80%在ASIC的输出端的VDD。如果在输出处观察到小信号ASIC*,有两种方法增加信号电平-减少负载(电容)C2或增加值RX。如果选择Rx的值等于XC2,谐振器处的信号幅度为½信号进入系统时钟。该添加Rx会降低晶体驱动电平,降低EMI并增加相移从而产生更高的可靠性,更稳定系统。

手机版

手机版