Raltron晶振公司常见的感应振荡器技术(三)

布置晶体和振荡器单元的振荡电路是比较复杂的,需要掌握相关的理论知识,和实操经验,以及会算了公式看懂公式,在这方面Raltron晶振公司做得比较好,注意石英水晶的研发,每年都投入大笔的金钱做为科研费用,并因此也为集团带来高收益。金洛鑫电子这几篇文章,都着重讲了晶振的感应振荡器技术,分为四篇,这是第三篇,最后一部分将会在下周一为大家献上。

在讲到振荡器的电路及相关资料的时候,总会提到电阻,电压,阻力,CL,电容,Q值,输出等词,这些都是振荡器电路上常见的专业术语,你可以在任何关于石英晶体振荡器的文章中可以看到,接下来也会围绕着这几个中心点,让大家更熟悉振荡器电路。

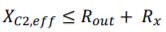

底线:设计大信号

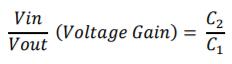

ASIC输出- 4伏特p-p,用于5伏逻辑。仅使用FET探头测量信号。从输出到输入的电压增益。从输出反馈的电压电平通过被动元件输入可能小于或大于信号输出。乍一看,这可能听起来很奇怪该信号可以通过增加被动元素;但是,如果门输入具有高阻力,可以证明输出信号正在为水箱上的水龙头充电电路和无源电压增益是大约等于C2/C1。

为了验证被动增益现象,在上放置一个非加载范围探针输入单元格(与C1相同)。去掉C1。观察信号增加直到ESD二极管限制信号。底线:弥补信号损失通过晶振,选择:

![]()

反馈电阻。反馈电阻用于偏置逆变器的输入A类配置。的大小电阻应足够大以防止加载反馈网络并允许逆变器在其中心运行范围。

对于基本模式和泛音带有储能电路的振荡器,R1应该是高频时0.5到1.0兆欧姆在较低的1至5兆欧姆频率。对于无感应器的第三泛音,选择更重要,只有少数几个千欧姆。

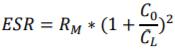

指定石英晶体。系列还是并联?平行!抵抗性。低晶体电阻期望更好的稳定性和更高的可靠性。低电阻晶体也是与成本成反比。对于并联谐振晶体,电阻应指定为有效系列阻力(ESR)。

其中Rm是运动阻力,C0是静电电容和CL是负载抵抗性。底线:阻力应该是指定尽可能低,实际上可能包括经济因素。负载电容。对于并联共振晶体,负载电容必须指定-假设您知道负载。这不是“首先出现的-坑洼或轮子?“情景。振荡器设计应该指明什么类型应购买组件。该订购或库存的水晶不应该决定振荡器设计。

虽然CL选择的更多细节是在下一节中,水晶是一般指定为12至20pf,CL这种类型的应用程序。振荡器设计细节。警告。以下元素值是建议可能需要的起始值迭代并要求测试。

测试。测试应该在a上进行模拟最终产品的面包板。应用启动电压应该包括缓慢的上升和步骤功能(这可能需要删除PCB供电电压并施加VDD外部可变电源)。在电源缓慢斜坡测试期间泛音,人们可以期待这种操作将是基本的,直到供应达到约2.5伏特。更正

较低模式启动通常由降低C2的电容值。两者的电源步进功能测试基本和泛音设计需要瞬间施加电力。这个可以通过提升ASIC VDD引线来完成并将其接触到VDD。这个测试应该包括ASIC的所有电压绝对最大值-通常为7.0伏特。

在高压阶跃功能测试期间,石英振荡器可能会尝试跳到下一个更高的模式。这是不可接受的条件。更正通常包括增加C2的价值。

负载电容。负载电容是指定为放置的电容与水晶的引线平行,会导致振荡器工作在f0。PCB流浪电容和ASIC输入/输出电容有助于负载。

C1和C2彼此串联。计算C1和C2需要杂散电容必须添加到所有计算。典型的配置有大约10pf的杂散电容输入和输出。对于初稿,计算负载电容没有任何流浪的住宿,输入或输出电容。如果设计C1和C2的计算指定10pfCL,使用15微升水晶。C1和C2将使用5pf计算假设。

共通电路选择。图7显示6种用于ASIC贴片晶振的常见设计振荡器操作。第一个电路(A)用于基础- AT和BT削减。电路(B)是首选弦外之音。偶尔使用电路(C)(D)和(E)-但不是本作者推荐的。

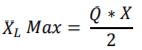

电路(F)是(B)最高的替代如果(B)的驱动程序是泛音频率有限。基本模式设计。该基模振荡器的操作电路中显示(A)一直很好记录(4),(5)和(6)。建议值列于表II中。可以理解无电感器方法通过观察分流的影响具有低值电阻的贴片石英晶振。一个并联谐振电路,电感和电阻具有电抗阻力图如图8所示那个电路的最大电感可以产生-3dB点并且有一个的价值。

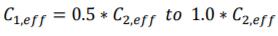

并联谐振电路的Q是定义为并联电阻除以要么是电抗:

![]()

重新排列:XL Max=R/2。在图9中,并联谐振电路的电感器取而代之的是晶体的电感。为2个分流值生成一个图抵抗性。我们观察到我们可以缩小圆的直径,因此最大可达到的电感值。

抑制基本模式和在3号操作,分流电阻(R1)必须降低。图10说明了用途一个2000欧姆的分流电阻器晶体,带5pf负载电容。注意矢量“B”在10MHz时为-j3000欧姆。晶体的电抗无法提供+j3000欧姆(极限为R1/2),如图所示矢量“A”是相同的幅度和与矢量“B”相反的相位。振荡根本不会发生。

对于第3次泛音,现在加载相同的5pf具有-j1000欧姆,如矢量“D”所示。矢量“C”具有相反的相位相同的幅度。现在是巴克豪森的阶段标准已得到满足和振荡器只能在f0=30MHz下运行。

负载的电容电抗会在第三个泛音减少1/3;该需要的感应电抗量也减少了1/3。如果巴克豪森的阶段标准要求a从谐振器给出感应电抗在基本模式下运行,并且适当值电阻并联放置用水晶,它会减少量感应电抗低于期望值由负载电容建立。

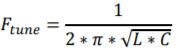

系列陷阱的泛音。泛音带有系列陷阱的振荡器是皮尔斯组态。基本陷阱是一个额外的系列L/C电路位于输入或单元格的输出。该系列引起共鸣组件是从基本计算的方程:

陷阱位置的选择是可选的。如果找到在单元格的输入端,Q值会很高-实际上是电感器的Q值。如果陷阱Q将位于单元格的输出上低-有效输出阻抗细胞+Rx除以细胞的电抗电感器。在输出上定位陷阱也倾向于在它之前清理信号进入水晶。

如果陷阱是,转动陷阱是非常关键的在单元格输入中。电感器通常是±10%的值。确定陷阱是适当调谐,电容应该是可调。确保陷阱保持调整过温,电容应该有负温度系数等于电感的那个。可能是一个小电阻与电感串联添加以降低Q到20并消除了这些问题。

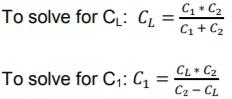

现在是“有效电容”一词适用于输入或输出腿系列陷阱。注意上面的共振,a系列陷阱变得归纳并且在与C1并行。电压增益现在C2,eff/C1表示输出端的陷阱或C2/C1,eff对于输入腿的陷阱。单元输出具有标准Rx相位移位电阻。C2遵循输出阻抗规则表IV和V是建议值。

平行坦克的泛音。该带有并联槽的泛音石英晶体振荡器也是皮尔斯配置,细胞输出具有标准的Rx可选相移电阻,必须使用电阻计算电抗油箱腿的有效电容。

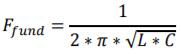

并联反谐振电路可以是位于输入或输出中细胞。通常情况下,更好的选择输出(最好过滤不需要的模式在水晶之前)。并联共振电路应调整为25%至50%两者之间的频率距离基本和第三个泛音。如果调整到更接近基频,电路将更有效第三次泛音频率的电容。如果调整得更接近中途距离,那么电路将具有更高的增益并且更容易启动。并联谐振元件是根据基本方程计算表IV和V是建议值。

注意:该电路在许多情况下也是可以接受的五泛音设计。BODE PLOT ANALYSIS。分析选择的反馈电路被执行使用微帽电路分析程序。图11,12和13是图的曲线图无电感泛音器(图7,电路B)在50MHz。图14是相同的晶体电路F.图15和16是电路F.30MHz。图11显示了对值的响应表III,在50MHz下具有25欧姆晶体。对于具有1纳秒延迟的逆变器,相位需要换档是180-18或162度。信号损耗约为4dB。

图12显示了更改Rx的结果到150欧姆。注意相变的变化率在162度地区更陡峭,该阶段将继续增加10度;然而损失是一个额外的2dB。图13显示了图12的校正随着C1减少到5pf。Rx还在150欧姆。这个情节非常相似原图11.除晶体负载外计算,Rx和C1是50的交易兆赫。

图14是电路F中的相同OSC晶振具有表VII的值。注意电路有更快的变化率,因为反馈电阻增加了。图15显示了40欧姆的响应,电路中的30MHz晶体F.组件除Rx为a外,其值按表VII列出短。操作点将接近180度;但是,阶段性变化率不是很陡峭。信号损失很小。图16安装了300欧姆Rx和C1减少到10pf。注意信号丢失是大致相同;然而相移在180度时更快点。Rx和C1互换增加了收益增加的变化率。摘要。对于基础应用程序,选择电路“A”。对于泛音,选择“B”或“F”。布局全部Rx的电路。大信号设计ASIC输出。使用Rx减少信号在水晶上,防止装载ASIC输出。保持C2,净值大于C1,净值为弥补水晶损失。检测结果。

手机版

手机版