关于Pletronics Crystal你不知道的事

美国Pletronics,Inc.公司成立于1979年,总公司在华盛顿州,今年是Pletronics晶振品牌成立的四十周年,几十年来Ple一直致力于石英水晶组件的开发与设计,产品种类有:32.768K,MHZ晶体,SPXO振荡器,TCXO晶振,VCXO晶振,VC-TCXO晶振,LV-PECL/LVDS差分晶振和OCXO振荡器等频率控制元器件。在北美,欧洲和亚洲都有生产工厂,在2011年的时候独立研发出LC振荡器技术,并获得业界的认可,Pletronics晶振公司多年来已创新了多项技术,开发性能高,成本低的振荡器,以下是Pletronics公司产品常见的一些问题解答,和技术资料。

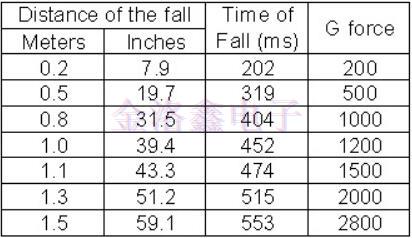

冲击水平和破碎的晶体导致故障:

石英晶体和石英晶体振荡器最常见的故障之一是破碎的晶体,包装内的晶体悬浮在包装内的自由空间中,悬浮在干燥的氮气中或抽空的空间中。高冲击会导致精密定时元件断裂。大多数Pletronics产品的额定功率为1500Gs,通过将设备放在地板上可以轻松达到这种水平的冲击。该图表显示了将物体放在硬木或乙烯基型地板表面上时达到的G力。混凝土地板上的力要高得多。

建议PCB/PWB焊盘几何形状:

随着无铅处理和RoHS的到来,Pletronics Crystal停止推荐晶体和振荡器的焊盘设计,以前整个电子行业都在使用铅锡焊料,而Pletronics可以根据这一一致性要求提出建议。今天,我们有许多不同的工艺,许多不同的助焊剂,许多不同的工艺温度。再加上这种复杂性,人们担心焊点会产生化学成分。例如,我们的陶瓷晶体和振荡器在镍焊盘上镀金以确保可焊性,对于一些最终用户而言,担心在完成的焊点中产生的金浓度。最终用户必须在考虑Pletronics焊盘,PCB/PWB焊盘尺寸,PCB/PWB上的任何镀层和焊接屏幕厚度的同时,决定使其工艺可靠地运行的原因。Pletronics确实在数据表上提供准确的封装焊盘信息,以帮助确定正确的PCB/PWB设计。

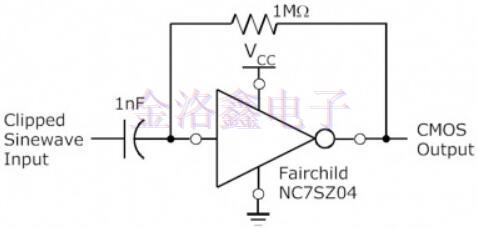

将削波的正弦波输出转换为CMOS:

来自许多TCXO晶振和其他振荡器的限幅正弦波输出信号很容易转换为CMOS输出信号,这个简单的电路可以由额定为0.8VPP限幅正弦波输出的振荡器驱动,规定最大负载为10K欧姆,与10pF并联。输出的CMOS方波具有VccPP电平,占空比接近50%,该电路工作电压范围为1.65V至5.5V,电源电压最低时为70MHz。将限幅正弦波转换为CMOS的成本很低,例如,2009年3月,一家全国知名的电子产品分销商以5K的数量将Fairchild逻辑门列为0.052美元ea。Fairchild逻辑门采用SOT23-5和SC70-5封装,其他组件总价不到0.01美元。

总抖动:

Pletronics Crystal报告数据表中的总抖动,总抖动是确定性抖动和随机抖动的总和,对于非倍增晶体振荡器(使用基模或第三谐波谐振器的振荡器),确定性抖动通常小于0.01pS。

为什么TCXO会剪切正弦波输出?

大多数陶瓷LCC封装的TCXO温补晶振仅适用于削波正弦波输出,这样做有很多原因,尽管它让许多想要CMOS输出电平的电路设计者感到沮丧,CMOS输出会为TCXO IC增加显着的功耗,IC和封装中产生的温度梯度将限制实现最佳TCXO补偿的能力。各种可能的CMOS负载会改变补偿设计,因为内部热梯度会导致TCXO不符合规格,当输出电平变化时,CMOS输出会导致电源和接地瞬变。这种噪声会对TCXO的相位噪声性能产生不利影响。CMOS输出产生更大的EMI/RFI信号,这可能导致难以满足美国FCC和其他国家从最终系统辐射能量限制的困难,截断的正弦波既是低振幅又大部分是正弦波,导致低信号电平和较少的谐波。使用这些TCXO的许多应用都具有ASIC输入,可接受限幅正弦波并在内部转换为CMOS逻辑电平。

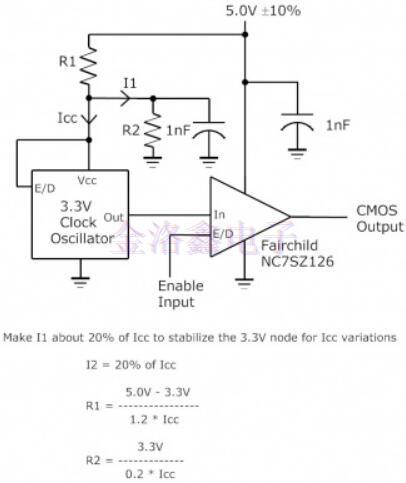

需要5.0V时钟-使用3.3VCMOS时钟:

5V CMOS石英晶体振荡器的可用性正在下降。这是使用现成的3.3V时钟振荡器的解决方案,Pletronics SM33xxT,SM44xxT,SM55xxT,SM77xxH和SM77xxD系列3.3V振荡器可与此电路配合使用,以满足5.0V时钟振荡器的需求,产生的信号特性将等于或优于旧的5V时钟振荡器,飞兆半导体NC7SZ126三态缓冲器随时可用,1K体积成本约为0.055美元。

LVDS驱动多个输入:

LVDS输出差分晶振可以驱动多路输入。

为什么水晶的频率限制较低?

晶体的厚度决定了频率。对于AT切割晶体,0.001“(0.0254mm)厚度约为63MHz基模谐振器。如果厚度加倍,则谐振频率将为0.5*63MHz或31.5MHz。8MHz晶体厚度为0.0078“(0.200mm).4MHz晶体厚度为0.0157”(0.400mm)。遇到两个限制特定包装尺寸中最低频率的条件:

1)简单的条件,较新的薄型陶瓷LCC封装不接受较厚的晶体。根据封装,频率下限范围从8MHz到12MHz,向下。

2)请记住,石英晶体谐振器是一种振动机械装置。对于最佳设计,那些具有较低ESR(CI)和无扰动(引起频率跳跃的不希望的振动模式)的振动区域应位于晶体的中心区域。当晶体频率较低且晶体较厚时,振动区域更加机械地耦合到边缘。在这种情况下,扰动(不需要的共振)变得难以控制。解决方案是使水晶倾斜或勾勒出轮廓(使水晶看起来更像放大镜的凹形)。边缘的这种变薄将振动区域限制在晶体中心并允许控制扰动。

不幸的是,限制振动区域会显着增加ESR。例如在12MHz:

SM13T5x7mm晶振ESR最大值为50欧姆;SM11T3.2x5mm晶体ESR最大值为80欧姆;对于这个例子,低于12MHz的SM11T不实用,因为ESR变得非常大。

精细泄漏测试标准:

测试条件:氦爆炸浸泡时间:7200秒(2小时)

轰炸压力:75psig

拒绝标准:>5.00-8atm.cc/sec

相位噪声到抖动转换:

OSC晶振抖动性能通常在频域中测量为相位噪声,因为该方法的精度和分辨率提高了,MaximSemiconductor做了一个出色的应用笔记,描述了相位噪声测量到抖动值的转换,这包括一个易于在EXCEL中实现的简化版本。

确定性抖动:

可预测的抖动分量称为确定性抖动。对于非倍增石英晶体振荡器,确定性抖动通常小于0.01pS。

PN中带有“S”的陶瓷封装振荡器:

许多Pletronics较旧的振荡器部件号在部件号中都有字母“S”。例如,SM7745HSV-25.0M。该“S”用于表示该部件被指定为满足45%至55%范围的逻辑高电平占空比。标准规格适用于40%至60%的占空比范围。随着技术的进步,用于制造石英振荡器的集成电路实际上都达到了45%至55%的范围,无需任何测试或筛选。事实上,Pletronics的所有陶瓷封装振荡器都达到了45%至55%的占空比范围。

由于“S”没有官方含义,因此从陶瓷部件的所有部件号中删除了。例如:SM7745HSV-25.0M与SM7745HV-25.0M相同,两个部件的高电平占空比均为45%至55%。其中带有“S”的部件号被接受为旧部件号,但没有特殊含义。

以上问答都是来自全球部分用户对Pletronics Crystal的问答,及PLE公司给予的回复,内容都是关于石英晶体和晶体振荡器系列的一些性能,特性,功能问题,是广大工程师可能要了解的一些关于石英水晶组件的知识和资料。如果你还有想要了解的晶振问题,欢迎到金洛鑫官网留言,我司会在最快的时间给出准确的答复,详情可登录http://www.quartzcrystal.cn/,期待广大新老客户的提问!

手机版

手机版