差分振荡器传统HCSL和低功耗HCSL之间的终端区别是什么?

差分振荡器传统HCSL和低功耗HCSL之间的终端区别是什么?

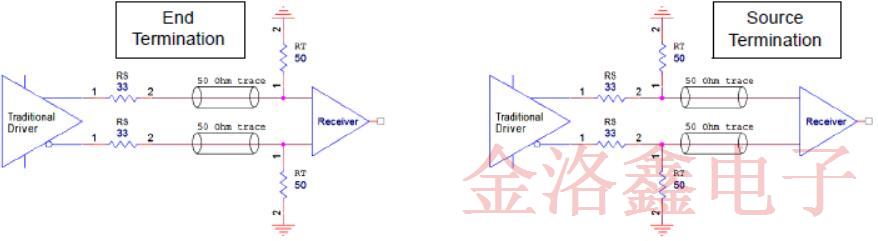

传统的差分晶振HCSL端接使用50Ω电阻在PCB走线末端接地.后来,引入了另一种方法,将50Ω接地放置在驱动器附近.这称为源端接,它允许时钟通过连接器,该连接器在电路处于活动状态(热插拔)时可以拔出.LP-HCSL按照定义在驱动程序端具有终结点,并且可以与终结点终结点一起使用.此设置称为双端接.源端接与端接对接收器没有影响.需要串联电阻RS以避免过多的振铃.

传统HCSL终止

LP-HCSL终止

现在,在驱动器附近,端接电阻(RS)与时钟线串联.驱动器本身设计为具有17Ω输出阻抗,因此需要另外33Ω才能匹配50ΩPCB走线.右侧的原理图带有端接电阻集成,因此不需要外部组件来驱动50ΩPCB走线.

传统的HCSL并不将驱动程序本身用作终止的一部分.除了50Ω终端电阻之外,传统的HCSL需要一个额外的33Ω串联电阻,以避免驱动器和50Ω端接走线之间的反射和振铃.P-HCSL概念在同一33Ω串联电阻中结合了避免主端接和振铃的功能,从而减少了低电压差分晶振数量计数.某些应用使用85Ω差分走线(或42.5Ω单端).对于这些应用,我们建议RS=27Ω.IDT它还提供集成了用于85Ω系统的27ΩRS的时钟.

双重终止:某些接收器可能有芯片中的差分终端电阻.这些接收器是通常更通用,可以处理各种幅度和共模电压,并且可能需要交流耦合时钟信号.LP-HCSL驱动器可以轻松驱动双端接.在源极和源极都有终端电阻接收器将每个引脚的幅度降低至约400mVpp(差分为800mVpp).通常这种类型不是问题接收机以较小的幅度工作.400mVpp(800mVpp差分)电平甚至超过了150mVpp(300mVppPCIe参考时钟的差分输出振荡器)输入摆幅规范.

差分振荡器传统HCSL和低功耗HCSL之间的终端区别是什么?

手机版

手机版