应用于高速数字时钟模块的低抖动晶振方案

高速的数字时钟模块能使现代化产品提升效率,如何让数字模块更加精准稳定,是众多工程师和科学家多年来一直在破解的难题,如今的高速数字时钟模块技术,足以满足需求.是科技是不断进步的,未来会需要更高效的数字时代模块,很早之前,海外的工程师就发现了,具有低相位抖动特性的有源晶振,可以给予模块更可靠,更稳定的时钟信号.

数字时钟设计的挑战:

为当今的高速数字电子设备设计时钟生成和分配系统给设计界带来了许多挑战.在较高速度下,传输线及其组件的行为与较低速度下的行为不同,如果没有正确指定和配置,则会产生抖动,噪声,反射和串扰等信号完整性问题.因此,当设计人员接近将具有高速数字应用的项目时,他们必须考虑在低速应用中不必要的各种信号完整性规定.

规划高速数字项目的主要挑战包括:

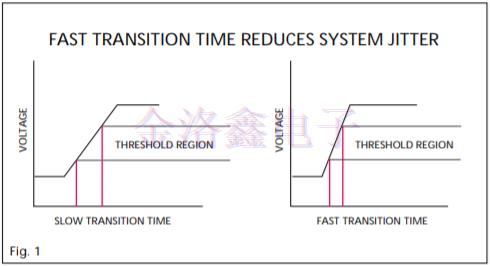

最大限度地减少定时抖动.对于高速,高频电子设备来说,具有低定时抖动至关重要.较差的石英晶振抖动特性不仅会影响数据错误,还会导致使用此源作为参考的锁相环失败.如果要将源用作显示时钟参考,则结果将是模糊的显示.通常,信号在过渡区域中移动得越快,产生的系统抖动就越少(参见图1).

减少排放.在高速应用中,产生电磁干扰(EMI)的可能性显着增加.随着数字速度的提高,有关EMI降噪的FCC规范变得越来越严格.设计人员需要解决诸如传输线,差分信号,信号幅度和谐波含量等特性,以便最大化传递给负载的能量,从而减少能量发射量.确保稳定.通常,您设计的电子系统的指定工作频率越高,时钟稳定性就越重要.无论是时钟性能不稳定都会导致数字系统中的误码率,错误数据或数据丢失

它们是本地或广域系统:传输线阻抗匹配.必须测量整个传输线的阻抗和长度,并与每个终端匹配.如果忽略阻抗匹配,则可能发生发射,串扰和反射.电源考虑因素.这里的主要考虑是确保时钟无噪音.对于当今更高速的系统,低电源消耗要求也在增加.

在高速应用中实现最佳系统性能的关键始于一种有效的时钟生成和分配设计方法.简而言之,设计人员应采用一种方法,将各种时钟生成和分配组件作为一个完整的解决方案,而不是单个部件.应在项目开始时仔细注意选择适当的部件和电路分配方法,同时牢记各部件之间的相互关系.此外,重要的是在设计进行时考虑操作频率下所有有源晶振和无源晶振元件的特性阻抗.

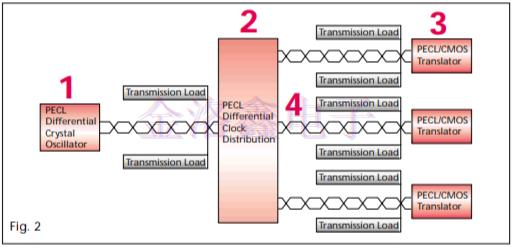

正确选择以下时钟生成和分配组件至关重要(参见图2):

1.石英晶体振荡器及其输出逻辑

2.时钟驱动程序,在某些情况下将包含启用功能

3.5V或3V电源的CMOS转换器

4.传输线(双绞线,同轴电缆,PCB走线)

时钟生成和分发组件注意事项:

1Crystal振荡器和逻辑选择选择合适的晶体振荡器在高速应用中至关重要,因为它将为整个时钟分配系统提供时钟参考.

严格的贴片振荡器应用通常要求频率稳定性为±20ppm,快速上升和下降时间小于600皮秒,低特性抖动和正发射极耦合逻辑(PECL)差分输出.频率稳定性将提供可靠的系统参考,而波形的快速上升和下降时间将导致低系统抖动.(虽然快速上升和下降时间使转换饱和可能会引入不必要的噪声,但这种噪声将通过使用差分信号来抵消.)

逻辑选择:PECL优势

在高速应用中,使用PECL逻辑输出提供了超过CMOS逻辑输出技术的关键优势.CMOS技术不同,PECL技术具有差分输出,这对减少排放至关重要.然而,与CMOS一样,PECL从正电源(而不是为ECL逻辑技术供电的负电源电压)获得其工作功率,从而在负载点实现与CMOS逻辑接口的必要兼容性.

此外,PECL技术允许电压补偿,以进一步抑制正电压源上的噪声.所有现代PECL器件均包含片内带隙调节器,可针对电源电压以及结温和环境温度的变化提供噪声容限的电压补偿.由于PECL电路由通过转向逻辑切换到负载电阻的电源调节电流源组成,因此设计人员可以通过两种方式获益:

1)供电电流随工作频率保持不变

2)AC性能随电压,温度和频率保持不变

可以实现相对于电源电压的水平,阈值和噪声容限小于1mV/V的残余灵敏度.对于结温,对于相同的参数,实现小于0.1mV/C的残余灵敏度.

晶体振荡器质量:

除了确保波形中的低抖动外,设计人员还应确保振荡器本身的抖动最小化.这是通过选择包含非常高Q晶体的振荡器来实现的.此外,晶体应调谐到振荡器电路以供振荡器制造商优化.应避免在振荡器设计中使用PLL合成器,因为抖动是由锁相环中的噪声产生的.

其他振荡器注意事项:

在PECL系统中,所有晶振电路都应使电源在振荡器处良好地去耦.PECL器件需要积极地解决此问题,因为PECL仅参考电源的最正面.因此,对于PECL,Vcc需要尽可能无噪声.由于振荡器特性确实随负载阻抗和负载偏置电压而变化,因此必须指定所使用的实际负载并将其传达给振荡器供应商.

所选时钟晶体振荡器应具有至少45%最小值和55%最大值的紧密对称性,并应产生可重复的波形以确保信号一致性.应使用地平面(参见“设计细微之处”部分).2Clock驱动器/分配注意事项时钟驱动器应该是PECL差分-设备-具有用于接收振荡器信号的差分输入,以及用于在PCB上分配信号的差分输出.如果需要时钟门控,应该有一个Enable引脚,可能是单端的.时钟驱动的另一个方面应该是器件的结构对称性,这将反映出更好的整体信号完整性.当迹线长度和/或衰减要求时,可能需要再生缓冲.重建结构非常重要,因为接收到的信号已经稳定下来并且仍然处于上升或下降的边缘.否则可能产生进一步的衰减而不是信号缓冲.

相关新闻动态

- 瑞萨半导体R-CarGen5驱动SDV技术创新的新引擎

- Renesas瑞萨新品推出物联网与智能家居的双功能微控制器

- 玛居礼HM系列晶振医疗设备小型化的可靠时钟解决方案

- Skyworks超低抖动时钟缓冲器领域的新标准开创者

- Suntsu松图VCXO压控差分晶振电子设备的频率魔法师

- QuartzCom专门从事自家生产的TCXO及VC-TCXO产品的制造

- Skyworks与Xilinx利用新推出的C波段频谱推动了5G技术的发展

- SiTime解锁导航航空航天与国防领域的精密时间密码

- 解锁KYOCERA京瓷晶振VCXO压控差分晶振电子世界的频率奥秘

- Raltron拉隆晶振为医疗设备制造商注入强劲动力

手机版

手机版