精密振荡器为高速串行通信链路实现了CDR

网络与通信已经成为城市最基本的基础建设,现代人也离不开信号网络,一颗高精密性的石英晶体振荡器,可以使网络模块设备,电信,高速串行通信链路等产品性能提升.现在普遍都是使用4G网络,但是目前5G通信即将覆盖,许多地方开始更换5G的无线基站,5G不仅仅是比4G多一个G而已,其速度将会是上一代4G的百倍.而且5G主要是应用到高端的操作,例如高速串行通信链路,时钟数据恢复,远程操控等.

时钟数据恢复(CDR)的应用在电信,光收发器,数据和存储区域网络以及无线产品中比比皆是.随着设计需要更大的带宽以及分配和频谱带宽使用的增加,CDR技术的优势变得越来越重要.此外,供应商及其产品正在从并行转换为串行接口,用于系统级和板级接口.近年来,CDR技术的使用越来越多,因为需要在背板上处理更宽的并行总线宽度,同时管理接收器的时钟和数据偏差.此外,路由这些信号可能很困难,因为它们消耗电路板空间和功率,并且需要多层路由方案来管理信号和线路终端.使用高位宽数据总线产生的EMI也是一个问题.

由于新通信技术的出现,电信号处理的改进以及跨FR-4和背板,光学和无线媒体发送多千兆位电信号的需求,CDR非常重要.在传输之前组合时钟和数据的通信技术并不新鲜.时钟和数据的组合确保时钟和数据信号始终同时到达.然而,诀窍是接收器处的时钟和数据的分离.这是由CDR电路完成的.将数据从并行格式转换为串行格式或反之亦然的产品称为串行器/解串器(或简称”SerDes”).这些产品通常具有CDR块以对串行数据流进行反序列化.

本文探讨了在高速串行通信链路应用中实现成功CDR所需的CDR组件模块.提供了关于如何通过链路转换和重新捕获数据的典型高速串行通信链路的概述.关于一般CDR拓扑讨论了不同的CDR方案.此外,还特别注意参考石英振荡器在链路的发送侧和接收侧的作用.

高速串行通信中的时钟和数据恢复

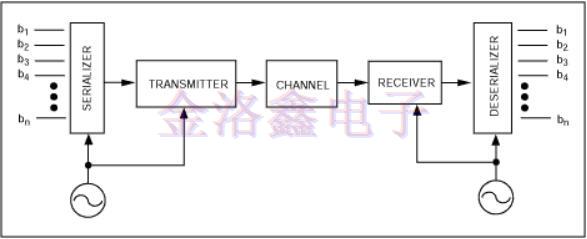

图1提供了高速串行通信链路的基本图.并行数据(比特b1,b2,b3,...bn)以频率ft到达传输串行器.在串行器内,数据从并行格式转换为串行格式.开发串行比特流,其最小比特率等于nxft,其中n是并行数据比特的总数.得到的频率(比特率)可以高于ft取决于数据是否被编码以满足误码率(BER)性能的信道要求或者在接收侧CDR提供丰富的转换内容.Reed-Solomon前向纠错(FEC)和8B10B编码分别是信道编码或在接收CDR处创建丰富转换内容的每个示例.然后准备该串行数据以便传输到信道并发送到接收器,最后到达解串器.该基本通信模块适用于数据,无论是通过光纤,空中还是跨背板传输.

图1.时钟和数据恢复是高速串行通信链路的基础.

时序(时钟)在CDR应用中至关重要.在系统设计期间,设计者确定如何将数据从并行格式驱动到串行格式,以便通过具有发送信号的未决信道失真的信道进行发送和接收.最大限度地降低设计降级对数据信号的影响对于保护信噪比和保持BER性能非常重要.例如,在背板的数字传输方案中,系统的抖动性能非常重要,因为高速电信号穿过各种长度(FR-4和背板),从而导致信号电平和时变信号降级扭曲.

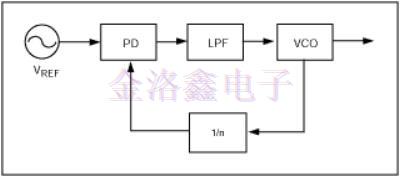

时钟数据恢复的核心是基于锁相环(PLL)的电路,在某些情况下可以基于数字.图2是可用于图1所示通信链路的串行器或发送侧的基本PLL框图.PLL模块包括相位频率检测器(PD),滤波器(LPF),压控晶振(VCO)和分割链(1/n).分频链用于向PD提供可比较的频率输入.通过这种方式,VCO的输出与非常稳定的参考输入VREF相位对齐.该PLL模块的目的是将参考频率乘以固定量(n),这将是VCO的固有频率.在大多数情况下,VREF将是基于石英的,提供高度的稳定性和准确性以及相位噪声特性.此外,根据所需的应用或系统要求,该参考可以是温度补偿或电压补偿.在基于SONET的应用程序中,此引用可能满足某个层级(即层级别3,3E或4).

图2.时钟乘法应用由PLL驱动.

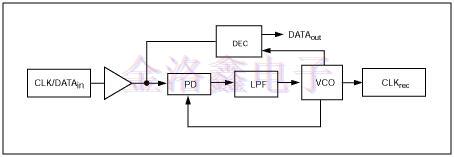

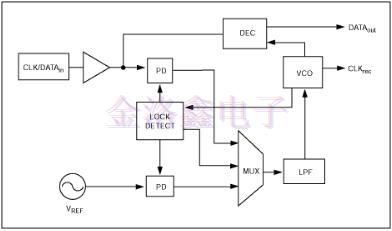

在接收端,CDRPLL模块具有略微不同的外观,以满足检索时钟和数据的需要.如图3所示,组合的时钟/数据信号通过缓冲器进入PLL模块,缓冲器为两条不同的路径供电.一条路径馈送数据决策(DEC)块,而第二条路径馈送时钟恢复块.时钟恢复模块看起来非常像图2的PLL模块减去1/n模块.来自VCO贴片振荡器的恢复时钟用作DEC的采样输入,反馈到相位-频率检测器,并且还用于向下游提供系统时序要求.在图1的情况下,该恢复的时钟被分频为并行时钟频率以驱动解串器块.

图3.基本PLL模块的修改用于实现CDR电路.

时钟/数据恢复中的参考振荡器

图中所示的参考振荡器说明了VCO被施加到振荡器的输入端.该电压控制由LPF级建立.通常,VCO或压控晶体振荡器(VCXO)可用作环路振荡器,如图3所示.主要作用是,环路振荡器需要跟踪输入时钟/数据的频率偏差.此外,它还为CDR(解串器)下游的其他组件提供此时钟.这是通过LPF的输出实现的,LPF驱动VCO或VCXO晶振的电压控制输入.

在用于电信,无线和数据通信的CDR应用中,输入数据信号加上时钟应具有相对稳定的频率特性.这假设发送时钟满足一定的精度和稳定性规范.在接收方面,设计排除了最小和最大精度/稳定性.如果传输时钟频率预计为规定频率的±50ppm,则接收时钟的频率调整能力至少为±50ppm.但是,出于设计目的,考虑频率调整能力略大于±50ppm.这种扩展的频率调整功能可以适应信道的任何额外信号频率失真或通信中断.

尽管PLL试图驱动静态条件,意味着已经建立了频率锁定,但可能存在电压控制输入可能以高于期望的速率移动的条件.LPF带宽决定了PLL可以保持锁定的最大速率.最终,接收VCO(或VCXO)的作用是跟踪和再现恢复的时钟.在没有数据/时钟输入到CDR的情况下,CDR在指定时间内需要为任何下游通信要求(即解串器)提供参考信号.

在某些应用中,将使用VCO/VCXO组合.在图4中,VCO/VCXO允许共同CDR配置至少有两个好处.首先,VCXO的添加允许快速调节VCO频率以匹配预期时钟/数据信号的频率.选择VCXO频率以匹配预期的时钟频率范围.例如,宽带VCO可能需要数千个样本才能锁定输入数据流.增加LV-PECL压控晶振和锁定检测电路可确保VCO保持一定的工作频率,并有助于在启动条件下提供更可预测的锁定时间.其次,如果时钟/数据输入在较长时间内丢失,则添加VCXO会很有帮助.在没有时钟/数据信号的情况下,系统会参考非常稳定的石英振荡器(VREF)提供保持,直到时钟/数据信号从信号丢失(LOS)中恢复.保持是一种规范,适用于参考时钟在一段时间内保持一定精度的能力(例如,24小时内为±4.6ppm).

图4.对基本CDR模块的修改可以轻松锁定传入的时钟/数据流.

各种解决方案可解决时钟/数据恢复和重定时,串行器和解串器,时钟发生器以及用于通信应用的TCXO晶振.这些器件允许设计人员开发频率范围从10MHz到10GHz的电路,并支持从GSM到OC-192及以上的应用.随着设计越来越需要更大的带宽,CDR技术非常适用于电信,光收发器,数据和存储区域网络以及无线应用.

手机版

手机版