EPSON Oscillator的PLL电路高频段输出实现方法

一直以来日本EPSON晶体公司,都是我国甚至全亚洲主要的频率元件合作商,50%以上的用户都是选择使用EPSON Oscillator或者晶体,因为EPSON曾在2010年获得全球晶体制造商排行第一名.其制造晶体振荡器的技术,也已达到领先的地步,近年来,EPSON公司一直在攻克PLL电路高频输出的实现方法,目前已成功应用到生产制造中,高端产品的”新陈代谢”促进电子元件行业不断的突破发展.

由于电影和其他内容传送服务的普及,数据传输速度和数量不断增加,以支持流经互联网骨干网的流量不断增长.对高速通信基础设施的需求推动了对提供稳定输出信号的高频参考信号源的强烈需求.一般来说,对于在高频下振荡的MHz切割晶体单元,晶体芯片的厚度必须减小(因为厚度决定了AT切割晶体单元振荡的频率)但是有限制关于加工方法,机械强度和易振性.虽然它取决于加工精度,但60MHz是对AT切割晶体的基频的限制.因此,爱普生定位超过60MHz作为高频范围.产生这种稳定的高频参考信号并不是那么简单,但爱普生有四种方法(技术)来实现高频振荡.

在第一种方法中,产生大约20MHz的相对可管理的振荡频率的AT切割晶体单元与倍频器电路或锁相环(PLL)电路组合以产生稳定的高频参考信号.产生高频,稳定参考信号的第二种方法是使用表面声波(SAW)谐振器,它以高频基频直接振荡.第三种方法是使用倒置-mesa型AT切割石英晶体单元,其中仅使用Epson的QMEMS工艺技术减薄晶体的振动部分.第四种方法是使用以AT切割晶体单元的高阶振动的振动模式(泛音).这些技术说明提供了第一种方法的概要说明,使用倍频器电路的方法(这里,乘法器电路是指提取谐波分量的模拟乘法器)和PLL电路.

1.倍频电路提供n度的高频输出

倍频器电路是将特定频率的电信号转换为增加到第n度的高频的电路.利用来自典型振荡电路的输出信号,形成一定水平的Tr,Tf,Voh和Vol产生包含谐波分量的波形.倍频器电路有意地产生强调来自这些谐波的第n个分量的信号,之后使用滤波器来提取第n个分量.使用谐波分量可实现比PLL更低抖动的输出频率.但是,当使用仅提取n次谐波的滤波器时,必须使用窄带宽/带通滤波器(BPF)来抑制低(n/2和更低)信号分量(子谐波)并限制抖动.此外,在选择晶体单元时和设计振荡电路时必须小心,以便源信号不会在n次谐波附近产生杂散信号.因此,用于获得高频的产品中使用的技术通常涉及PLL电路.

2.PLL电路

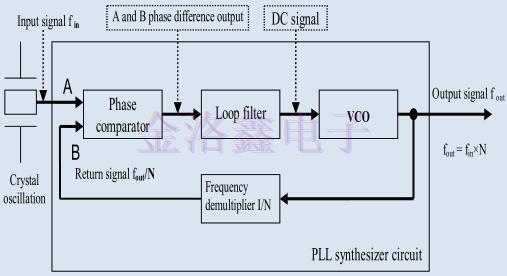

以下是PLL电路的说明,PLL电路是产生稳定的高频信号的另一种基本技术.随着包括无线通信组件的设备的传播,用于无线通信的半导体技术已经取得了显着进步.在这些技术中,PLL电路技术的创新尤其令人震惊.PLL电路产生与输入参考信号同步的输出信号.利用包括相位比较器,环路滤波器和压控振荡器(VCO)的基本结构,PLL电路能够产生与输入信号精确同步的信号.与倍频器电路不同,源信号不用于输出.PLL电路使用VCO以与源信号不同的频率产生同步信号.

通过在PLL电路VCO输出和相位比较器输入之间插入分频器,使输入信号和分频信号同步,将VCO输出控制为通过将输入频率乘以分频比而获得的频率.为了使该VCO输出达到与石英晶体振荡器相当的精度,有必要在使用可产生稳定输入信号的晶体振荡器或类似元件的同时改变分频比.这是频率合成器背后的原理.应用这一原理,AT切割晶体单元的MHz频带输出被输入到PLL电路,以产生生成GHz频带载波的信号,用于无线通信.

图1.PLL合成器电路基本结构

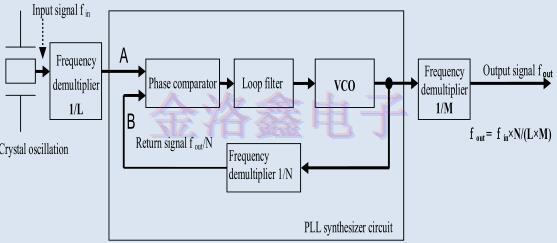

图2.将频率分频器插入输入的示例

使用PLL电路产生比输入频率高许多倍的高频的关键在于如何使用分频器.用于实现输入频率的n次输出的方法是图1中所示的电路配置.另外,如图2所示,在PLL电路I/O之前和之后插入分频电路允许精确调节输出频率.用于增加PLL电路中的频率设定分辨率的典型方法包括在晶体振荡源之后直接引入分频器.然而,使用较高的分频来增加频率设置分辨率会导致较低的相位比较频率,这导致PLL响应性和环路增益的下降.这反过来又对输出波形抖动和相位噪声特性产生负面影响.解决该问题的方法是使用例如分数PLL.

3.整数PLL和分数PLL的特性

PLL晶振电路主要分为两种类型:整数和分数.两种类型都使用振荡源输出高频信号.下面是对主要特性的解释.顾名思义,整数PLL能够产生输入频率的整数倍的输出频率.例如,如果要从1MHz源输出100MHz信号,则分频器计数器设置为100.相反,分数PLL能够产生输入频率的分数倍的输出频率.该电路的优点在于它允许您选择任何频率(使您能够获得精确的频率设置分辨率).分数PLL允许精确的频率分辨率设置,初始频率偏差可以通过这些属性精确控制.

然而,缺点是电路设计复杂并且与整数PLL相比IC的尺寸变大,这意味着倾向于发生特定的寄生.结果,通常认为分数PLL比整数PLL产生更多的相位噪声.然而,随着最近的技术进步,正在努力减少寄生的发生,迄今为止这一直是使用分数PLL的弱点.

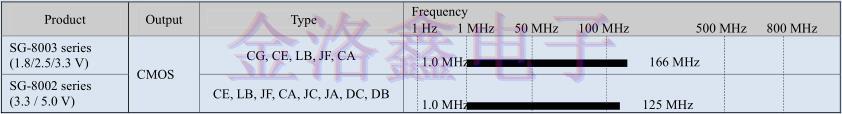

爱普生产品阵容和产品功能

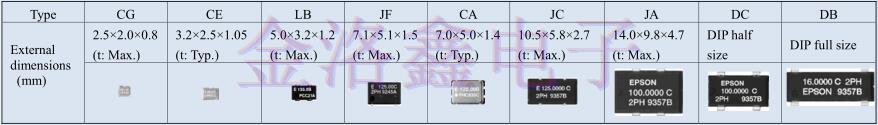

上面,我们研究了使用PLL电路作为实现高频输出的方法.这些方法的最大特点是能够随意创建所需频率.换句话说,这些方法可在您需要时提供必要的频率,包括高频.爱普生晶振的SG-8000系列采用上面介绍的整数PLL电路技术,提供各种形状和尺寸的多样化产品阵容(表1).我们还提供ROM编写器(SG-WriterII)作为编程工具,允许客户将频率命令写入SG-8000系列(表2).

SG-8000系列采用AT切割晶体单元.AT切割晶体单元的立方曲线温度特性保持了给定的温度稳定性,使我们能够提供具有平滑频率特性(无频率跳变)的产品,这些产品不需要在很宽的范围内进行基于温度的补偿.(具有显着温度特性的一阶线性度的石英振荡器,例如Si-MEMS振荡器,需要电路补偿以维持给定温度下的稳定性,并且可能导致频率跳变的发生.)

EPSON Crystal期待帮助客户体验这些晶体单元的高精度特性,以及通过PLL电路技术实现的自由频率设置的便利性.最后,下面提供了关于"倍增"和"PLL"作为用于实现高频输出的方法的一些注意事项.乘法:注意电路中产生的次谐波分量,以及低于n/2的分量引起的抖动.PLL:注意环路带宽,并在连接到后续PLL时注意抖动放大和跟踪.

表1:可编程晶体振荡器产品阵容

表2:SG-8000系列编程工具

|

|

SG写入器 |

|

连接器端子 |

usb2.0(最小b) |

|

兼容的操作系统 |

Windows7(32位,64位) WindowsVista(32位) WindowsXP(32位) |

|

插座 |

GS-8002,SG-8003 两个套接字都是可写的 |

|

软件 |

SG-WriterII软件 |

手机版

手机版