LVDS晶振驱动多个输入

差分晶振系列里比较常用的输出方式是LVDS,这是一种低电压的差分信号,主要应用于图像输出传送,高速度数据通信处理,网络程控交换等领域,它的电流传输数据是恒定的3.5mA,可以产生非常低的EMI消除共模噪声干扰,因此具备LVDS输出的石英晶体振荡器,通常都拥有低相位噪声性能。LVDS在输出信号的时候会使用交流耦合技术,这样是为了让交流耦合电容器隔断全部的直流分量信号,实现直流平衡,因为LVDS晶振还具备比较高端的低相位抖动功能。

本应用笔记介绍了如何将LVDS信号用于采用Virtex-EFPGA的高性能多点应用。多点LVDS允许许多接收器由一个Virtex-ELVDS驱动器驱动。仿真结果表明此处描述的参考设计将从DC运行到311Mbits/s。本应用笔记包括DC规格,微带线和布局指南。采用简单的源和差分端接,Virtex-EFPGA直接驱动多点LVDS,取代昂贵的TTL-LVDS驱动器和接收器,减少电路板面积和高性能应用的偏斜。

与其他LVDS驱动器相比,Virtex-E驱动器实际上提高了信号完整性通过吸收源处的任何反射能量而不是将其传递下来这条线。这项创新可实现多点线路上的311Mb/s信令多为20个LVDS接收器,在参考设计中跨越4英尺以上,具有高信号完整性和抗噪性。引言LVDS使用差分信号来提高单端噪声抗扰度技术。多点LVDS允许许多接收器由一个接收器驱动Virtex-ELVDS驱动器。真正的差分LVDS输入和输出能力Virtex-EFPGA支持这种多点应用。Virtex-E多点降落LVDS驱动器可以驱动具有20比1扇出的线路,从而制造出Virtex-ELVDS适用于各种高负载应用。Virtex-ELVDS驱动器消除了昂贵的TTL-LVDS转换器,实现了逻辑的直接接口高速差分信号。这种集成减少了信号偏斜和减少实现高性能应用程序所需的电路板面积。多点LVDS电路。

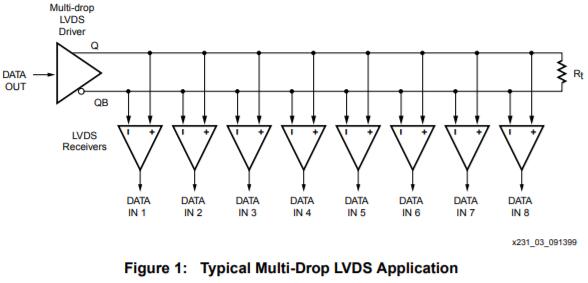

图1显示了典型的多点LVDS石英晶振应用。Q和Q输出左侧的LVDS驱动器串行连接到LVDS接收器的输入沿着多点线的长度。电阻器RT终止Q和Q.在多点线路的末端并行发出信号。简单的微带线在具有接地层的标准PC板上制造,足以满足此应用需求。

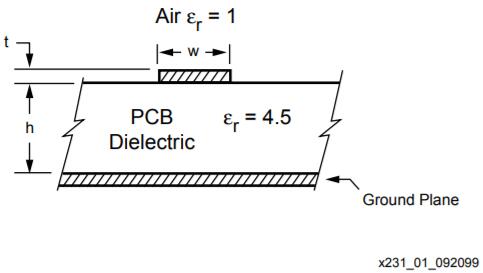

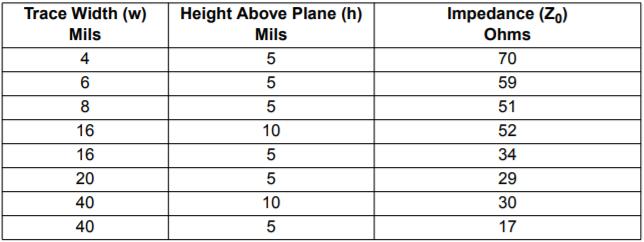

微带线是顶部或底部的PCB(印刷电路板)迹线PCB在下一个内层的地面或电源平面上。图2显示微带传输线的横截面。迹线宽度(w),迹线高于地平面(h)的高度,迹线厚度(t)和相对电介质PCB的常数(εr)决定了微带特性阻抗(Z0)。表1总结了微带的特征阻抗图2显示了使用1盎司铜的FR4PCB上w和h的典型值。

图2:微带传输线的横截面

表1:w和h的典型值的微带阻抗

笔记:

t=1.4密耳(1盎司铜)

εr=4.5(高频时的典型FR4)

1000密耳=1英寸=25.4毫米

阻抗误差=±2%

平面上方的迹线宽度和高度四舍五入到最接近的密耳易于布局和制造。注意微带传输线阻抗与w/h比大致恒定。w/h比率为4,给出大约Z0=29到30欧姆。w/h比为1.6,给出大约Z0=51至52欧姆。使用w/h比率近似,具有任何平面间距的微带的特征阻抗可以是估计。

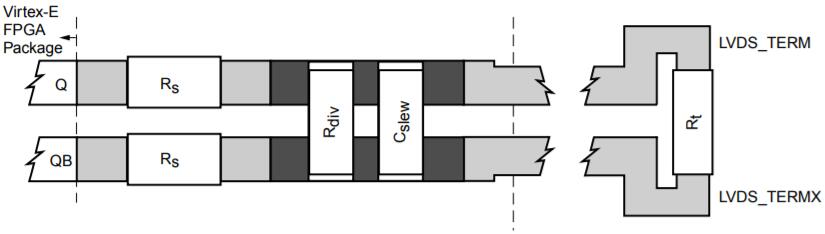

图3是带有源的Virtex-E多点LVDS驱动器的示例布局左边是电阻和电容,右边是终端电阻。

1.所示的所有PCB走线均为29Ω微带线。

2.可以使用与Rs和Rdiv串联的更高阻抗

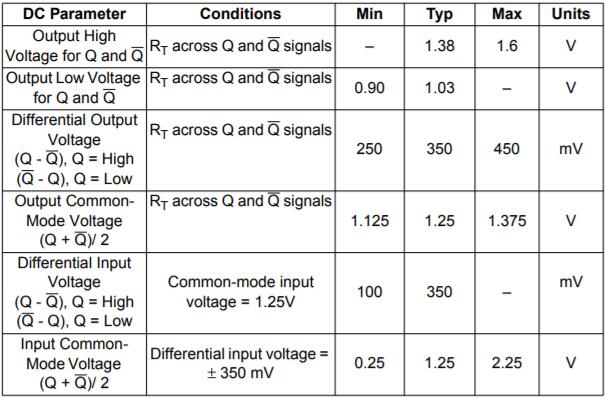

LVDS输出通常驱动±350mV的电压摆幅(Q-Q),并且Q和Q的平均值(Q+Q)/2有时被称为偏移电压或共模电压。典型的LVDS输出共模电压为1.25V,由LVDS驱动程序设置。有关多点LVDS的更多信息,表2总结了DCLV DS的规格。

表2:标准LVDS DC规范

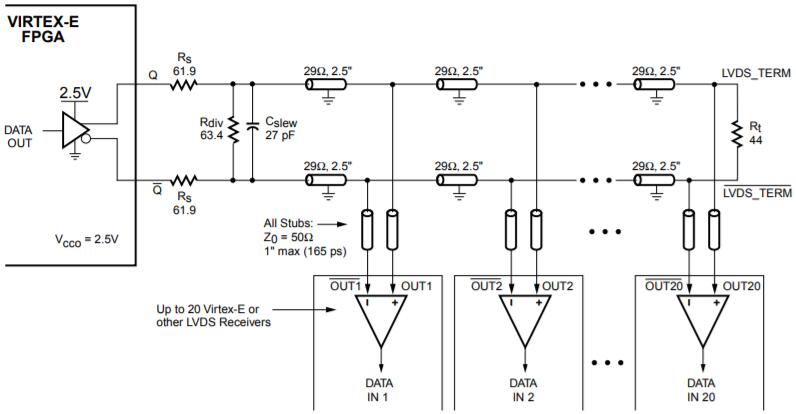

图4显示了Virtex-ELVDS线路驱动器的完整原理图以多点配置驱动20个LVDS接收器。接收器是Virtex-E接收器或其他现成的LVDS接收器。LVDS信号由左侧的Virtex-ELVDS驱动器驱动,并以菊花链形式连接两条29欧姆的传输线和短截线连接到所有20个LVDS接收器OUT[1:20]和OUT[1:20]节点。每个LVDS接收器每2.5英寸轻触主多点线路,多点线路长度为50英寸。每LVDS接收器抽头线具有1英寸的最大短截线长度和50欧姆传输线对地阻抗,或差分阻抗为100两个短截线之间的欧姆。放置一个44欧姆的终端电阻RT在靠近最终LVDS的LVDS_TERM和LVDS_TERM节点上接收器,在右边。电阻RS和RDIV衰减输出的信号VCCO=2.5V的Virtex-ELVDS驱动器,提供22欧姆源阻抗(串联终端)到29欧姆传输线。该设计由于增加了LVDS晶振的负载,因此需要22欧姆的源阻抗接收器将29欧姆线路降至22欧姆的有效阻抗一般。电容CSLEW降低了Virtex-E的压摆率LVDS驱动器,可以减少反射,减少接收器的振铃。

图4:Virtex-E20负载多点LVDS原理图

为什么一条29欧姆的传输线在两端用22端接欧姆终止?答案在于传输线的行为。当电容式接收器和短截线加载传输线时,额外的电容会降低有效阻抗。图4中的接收器有有效负载电容约为9pF,包括接收器电容,走线和短截线电容。一个9pF电容器,每2.5英寸放置一个29欧姆线将线路降至22欧姆。因此,反射是如果线路端接到22欧姆,则最小化。有关更多信息有效的传输线阻抗,见霍华德W.约翰逊,“高速数字设计:黑魔法手册,“1993,pp.172-174。关于等间距电容负载提供以下等式:

如果Z0=√L/C.

其中L=电感/单位长度

C=电容/单位长度

和CL=每个负载的电容

N=负载数量

H=传输线的总长度

然后Z0EFF=√L/[C+N*CL/H]

虽然传输线使用的阻抗比典型值低,在表2中使用的规范中发现的阻抗,所有的电压摆幅符合LVDS标准。这意味着任何LVDS接收器都可以工作正确地在这个多点线上。实际上,较低的阻抗会导致更宽的走线,从而减少沿多点线路的电感和趋肤效应损耗。两条29欧姆单端传输线可以是微带线,带状线,或单端等效的58欧姆双绞线或类似的平衡差动传输线。请参见Xilinx应用笔记中的附录A.XAPP230,“LVDSI/O标准”,用于讨论传输线和LVDS中使用的终端。多点Virtex-ELVDS线路驱动器符合所有标准ANSI/TIA/EIA-644LVDS接口标准DC输入电平如表2所示

输出共模电压通常平均为VCCO/2。组件价值RS,RDIV和CSLEW的推导可以在第10页的附录B中找到。Virtex-ELVDS的直流性能符合或超过表2中所示的ANSI/TIA/EIA644LVDS接口标准规范。图4中的Virtex-E多点LVDS终端与其他LVDS不同源终端,因为它实际上吸收了源处的反射能量。

虽然大多数LVDS驱动器的行为类似于具有高输出的电流源阻抗,Virtex-E多点LVDS线路驱动器的行为类似于电流源与22欧姆电阻并联,从而改善光源终止反射信号。22欧姆的源阻抗Virtex-ELVDS驱动器可以吸收几乎所有的差分反射容性负载沿多点线分布,减少了站立与其他LVDS驱动器相比,波浪,下冲和噪声水平。该LVDS_TERM和LVDS_TERM以及传输线上的电压达到或超过表2中所示的所有标准LVDS输出电平。

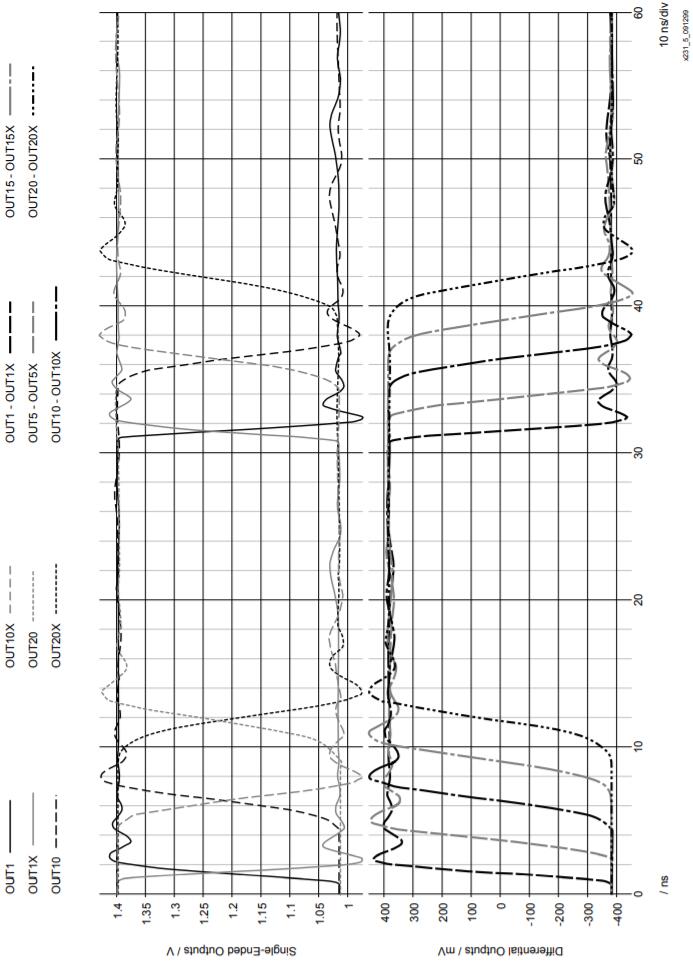

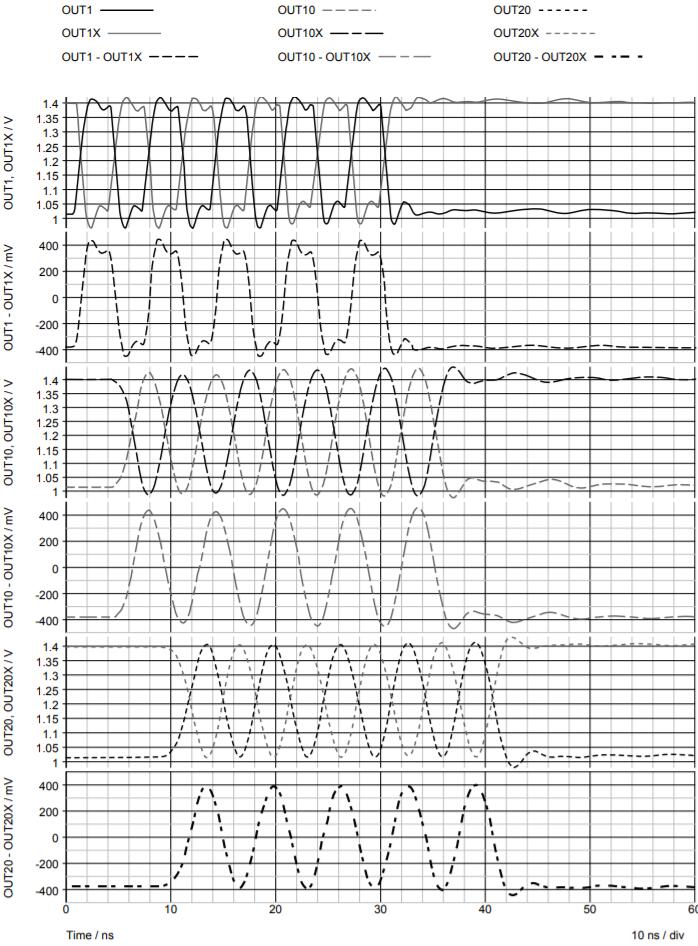

图5显示了Virtex-E多点LVDS驱动器的典型阶跃响应对于图4中的原理图,上图显示了单端输出1,10和20的波形,对应于输入端的接收器多点线的开始,中间和结束。下图显示了沿着多点线路的五个接收器的差分电压从开始结束。所有电压均在接收器的片上差分输入端测量。所有接收到的波形都显示出类似的特征,几乎没有下冲或过冲和负载反射可忽略不计。

图5:Virtex-E多点LVDS驱动器的典型阶跃响应

图6显示了典型的311Mb/s突发数据(或155.5MHz时钟)响应Virtex-E多点LVDS输出,用于图4中的原理图。单端并且沿着多点线示出了输出1,10和20的差分波形。所有接收的波形都显示出相似的特征,很少或没有下冲/过冲和可忽略不计的反射。一些平滑的波形发生在接收器加载的多点线的长度上,但衰减很小。即使最后一个接收器也能看到近400mV的峰值在19个其他接收器之后的50英寸线的末端。优秀Virtex-E多点LVDS的性能可归功于它的匹配源阻抗和源极上升时间减少电容器CSLEW。Virtex-E多点LVDS驱动器与LVDS接收器完全兼容。

图6:Virtex-E多点LVDS输出的典型311Mb/s突发数据响应原理图如图4所示。

Virtex-EFPGA发送和接收多点LVDS。最大值对于-7Virtex-E速度等级,数据速率为311Mb/s或155.5MHz的时钟。Virtex-ELVDS驱动器可显着改善信号完整性其他现成的LVDS驱动器由于其匹配的源阻抗而导致系列终止传输线并最小化源反射。可以为多达20个LVDS接收器提供可靠的数据传输电气长度为8.25ns(50英寸),仅受皮肤效应损耗的限制PCB走线。采用LVDS的Virtex-EFPGA消除了昂贵的TTL-LVDS驱动器和LVDS-TTL接收器,减小电路板面积,减少信号延迟偏差,同时可靠地传输长距离的高速数据和时钟芯片,电路板,机箱和外围设备之间。

Virtex-E多点LVDS电路的印刷电路板布局指南在图4中如下:

1)具有受控传输线的多层印刷电路板阻抗是必需的。

2)LVDS驱动器和接收器之间的所有传输线应该是参考公共地平面,除非通过平衡差分传输线,如双绞线。对于双绞线和其他平衡线,利用连接到地面的接地屏蔽在双绞线电缆的开头和结尾处的平面允许共模返回电流。如果没有可用的屏蔽连接,请额外使用注意使用对称和等长路由并确保容性负载平衡差分对以防止过多的共模差模转换。不要在信号下分割地平面因为这会导致电感增加导致大的不连续性。

3)电阻RS和RDIV应靠近Virtex-E输出Virtex-E多点LVDS线路驱动器。放置并联终端电阻RT接近多点线路远端的最终LVDS输入。

4)电容CSLEW应靠近电阻RS和RDIV。

5)应使用多点LVDS的对称和等长路由源和目标之间的信号对,以最大化共模拒绝。以两个LVDS信号之间的最小间距布线两个LVDS信号沿多点线和存根的迹线。如果迹线间距小于电介质厚度对地平面,差分阻抗的影响必须包括在内以确定有效的传输线阻抗跟踪阻抗将受差分阻抗的显着影响两条痕迹之间。较宽的间距对阻抗的影响较小。

6)Virtex-E为驱动和提供专用的LVDS输入/输出对接收LVDS。从单个时钟驱动的IOB寄存器提供了一个方便点同步输入和输出。

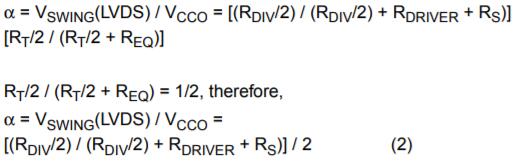

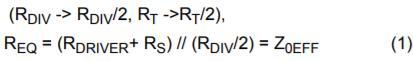

参考图4,电阻器RS和RDIV衰减出来的信号Virtex-ELVDS驱动器提供匹配的源阻抗(串联终止)到传输线。确定RS和RDIV的值通过这两个约束。等效源阻抗REQ,包括Virtex-E驱动器阻抗RDRIVER,必须等于有效传输线阻抗,22欧姆。使用差分半电路:

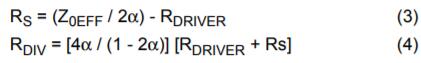

选择RS和RDIV以获得所需的信号路径衰减从Virtex-E驱动器到LVDS目的地。所需的信号衰减定义为α。

使用等式1和2并求解RDIV和RS产量:

代入Z0EFF=22欧姆,RDRIVER=10欧姆,VCCO=2.5V,和VSWING(LVDS)=380mV进入等式2-4并四舍五入到最接近的1%如图所示,发现RS=61.9欧姆和RDIV=63.4欧姆的值在图4中,350mV的典型LVDS电压摆幅增加到380mV在50英寸末端附近以311Mb/s的数据速率抵消趋肤效应损失多点线。

CSLEW增加了Virtex-E多点驱动器的上升时间。通常情况下,LVDS的10-90%上升时间为500ps。使用CSLEW,所需的上升时间为增加到大约1ns。使用等效的差分半电路图4,(RDIV->RDIV/2,CSLEW->2CSLEW),驱动点阻抗为2CSLEW是REQ//RT/2=REQ/2。RC时间常数是:(2CSLEW)(REQ/2)=REQCSLEW。

通过设置τ,RC时间常数,等于原始LVDS上升10-90%届时,新的10-90%的上升时间将近1ns。CSLEW的值是

计算公式为:

CSLEW=τ/REQ(5)

将τ=500ps和REQ=22欧姆代入公式5并进行四舍五入

得到最接近的10%值,得到CSLEW=27pF的值,如图所示图4。

差分晶振是石英水晶组件算是最高级的一种,使用的效果和意义是非常大的,而且随着全球大范围的重视科技,发展科技,产品变得更多功能化,复杂化,部分中高端产品需要差分晶体振荡器这种高性能,高稳定,高可靠性的频率元件支持。而且还在保障低电压效能,常用的是1.8~3.3V之间,耗能是非常低的,精准的识别小信号,分析处理“双极”信号,可能帮助产品阻抗外界的干扰。

手机版

手机版